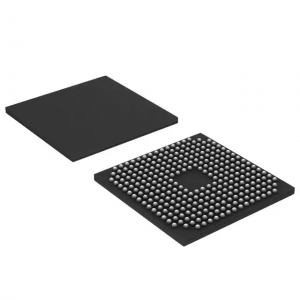

TMS320C6657CZHA IC DSP FIX/FLOAT POINT 625FCBGA

Product Parameter

Description

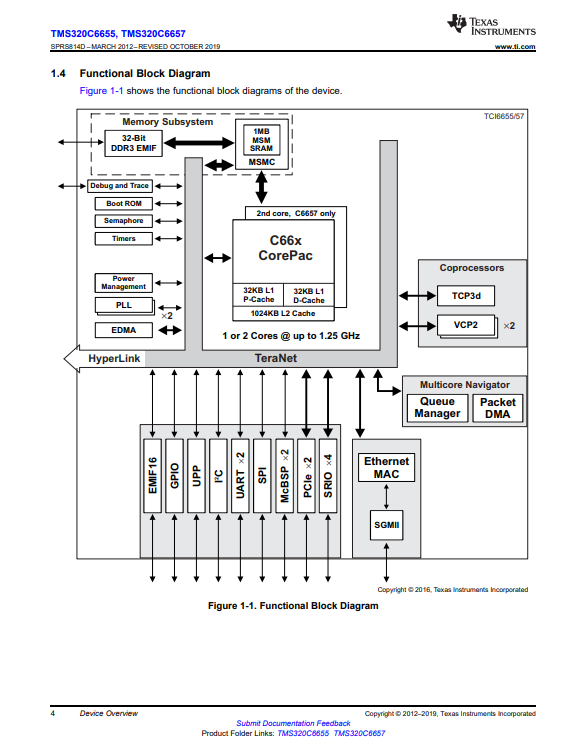

TI's KeyStone architecture provides a programmable platform integrating various subsystems (C66x cores, memory subsystem, peripherals, and accelerators) and uses several innovative components and techniques to maximize intradevice and interdevice communication that lets the various DSP resources operate efficiently and seamlessly. Central to this architecture are key components such as Multicore Navigator that allows for efficient data management between the various device components. The TeraNet is a nonblocking switch fabric enabling fast and contention-free internal data movement. The multicore shared memory controller allows access to shared and external memory directly without drawing from switch fabric capacity. For fixed-point use, the C66x core has 4× the multiply accumulate (MAC) capability of C64x+ cores. In addition, the C66x core integrates floating-point capability and the per-core raw computational performance is an industry-leading 40 GMACS per core and 20 GFLOPS per core (@1.25 GHz operating frequency). The C66x core can execute 8 single precision floating-point MAC operations per cycle and can perform double- and mixed-precision operations and is IEEE 754 compliant. The C66x core incorporates 90 new instructions (compared to the C64x+ core) targeted for floating-point and vector math oriented processing. These enhancements yield sizeable performance improvements in popular DSP kernels used in signal processing, mathematical, and image acquisition functions. The C66x core is backward code-compatible with TI's previous generation C6000 fixed- and floating-point DSP cores, ensuring software portability and shortened software development cycles for applications migrating to faster hardware. The C665x DSP integrates a large amount of on-chip memory. In addition to 32KB of L1 program and data cache, 1024KB of dedicated memory can be configured as mapped RAM or cache. The device also integrates 1024KB of Multicore Shared Memory that can be used as a shared L2 SRAM and/or shared L3 SRAM. All L2 memories incorporate error detection and error correction. For fast access to external memory, this device includes a 32-bit DDR-3 external memory interface (EMIF) running at a rate of 1333 MHz and has ECC DRAM support.

| Specifications: | |

| Attribute | Value |

| Category | Integrated Circuits (ICs) |

| Embedded - DSP (Digital Signal Processors) | |

| Mfr | Texas Instruments |

| Series | TMS320C66x |

| Package | Tray |

| Part Status | Active |

| Type | Fixed/Floating Point |

| Interface | DDR3, EBI/EMI, Ethernet, McBSP, PCIe, I²C, SPI, UART, UPP |

| Clock Rate | 1GHz |

| Non-Volatile Memory | ROM (128kB) |

| On-Chip RAM | 2.06MB |

| Voltage - I/O | 1.0V, 1.5V, 1.8V |

| Voltage - Core | 1.00V |

| Operating Temperature | -40°C ~ 100°C (TC) |

| Mounting Type | Surface Mount |

| Package / Case | 625-BFBGA, FCBGA |

| Supplier Device Package | 625-FCBGA (21x21) |

| Base Product Number | TMS320 |

Related PRODUCTS

-

Tel

-

E-mail

-

skype

-

whatsapp

whatsapp